Product Summary

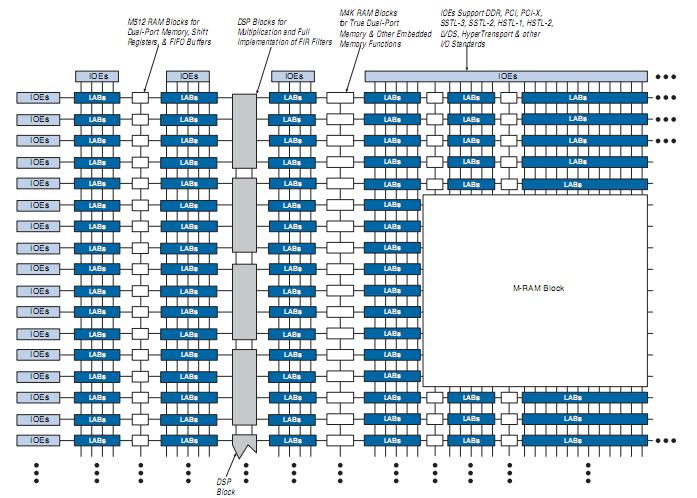

The EP2S30F672I4 is an FPGA. It is based on a 1.2-V, 90-nm, all-layer copper SRAM process and features a new logic structure that maximizes performance, and enables device densities approaching 180,000 equivalent logic elements (LEs). The EP2S30F672I4 offers up to 9 Mbits of on-chip, TriMatrix memory for demanding, memory intensive applications and has up to 96 DSP blocks with up to 384 (18-bit × 18-bit) multipliers for efficient implementation of high performance filters and other DSP functions. The EP2S30F672I4 also offers a complete clock management solution with internal clock frequency of up to 550 MHz and up to 12 phase-locked loops (PLLs).

Parametrics

EP2S30F672I4 absolute maximum ratings: (1)Supply voltage:–0.5V to 1.8V; (2)Supply voltage:–0.5V to 4.6V; (3)Supply voltage:–0.5V to 4.6V; (4)Analog power supply for PLLs:–0.5V to 1.8V; (5)Digital power supply for PLLs:–0.5V to 1.8V; (6)DC input voltage:–0.5V to 4.6V; (7)DC output current:–25mA to 40mA; (8)Storage temperature:–65℃ to 150℃; (9)Junction temperature:–55℃ to 125℃.

Features

EP2S30F672I4 features: (1)15,600 to 179,400 equivalent LEs; (2)New and innovative adaptive logic module (ALM), the basic building block of the Stratix II architecture, maximizes performance and resource usage efficiency; (3)Up to 9,383,040 RAM bits (1,172,880 bytes) available without reducing logic resources ; (4)TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO)buffers; (5)High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters; (6)Up to 16 global clocks with 24 clocking resources per device region; (7)Clock control blocks support dynamic clock network enable/disable, which allows clock networks to power down to reduce power consumption in user mode; (8)Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switch-over, real-time PLL reconfiguration, and advanced multiplication and phase shifting.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EP2S30F672I4 |

|

IC STRATIX II FPGA 30K 672-FBGA |

Data Sheet |

|

|

||||||

|

EP2S30F672I4N |

|

IC STRATIX II FPGA 30K 672-FBGA |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))