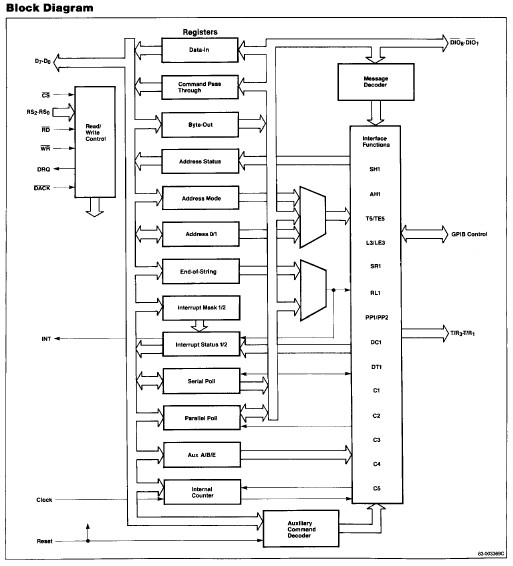

Product Summary

The UPD7210C is an inteligent, general purpose interface bus (GPIB) controller designed to meet all of the functional requirements for talker, listener, and controller (TLC) as specified by IEEE standard 488-1978. Connected between a processor bus and the GPIB, the controller provides high-level management of the GPIB to underden the processor and to simplify both hardware and software design. The UPD7210C is fully compatible with most processor architectures and requires only the addition of bus driver/receiver components to implement any type of GPIB.

Parametrics

UPD7210C absolute maximum ratings: (1)supply voltage, VCC: -0.5 to +7.0V; (2)input voltage, VI: -0.5 to +7.0V; (3)output voltage, VO: -0.5 to +7.0V; (4)operating temperature, TOPR: 0 to +70℃; (5)storage temperature, Tstg: -65 to +150℃.

Features

UPD7210C features: (1)all functional interface capability meeting IEEE standard 488-1978; (2)programmable data transfer rate; (3)16 MPU accessible registers: 8 read and 8 write; (4)2 address registers: detection of MTA, MLA MSA; 2 device addresses; (5)EOS message automatic detection; (6)command automatic processing and undefined command read capability; (7)DMA capability; (8)programmable bus transceiver I/O specification; (9)1 MHz to 8MHz clock range; (10)TTL compatible; (11)NMOS; (12)+5V singel power supply; (13)8080/85/86-compatible.

Diagrams

|

UPD70008AG-4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD70236AGD-10-5BB |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD7030025AGC-25 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD703014A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD703014AY |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD703015A |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))